半導体でのプロセスは集積回路などを製造していく工程のことです.本記事ではプロセス技術の概要とSimulation、ウェーハ製造工程について解説しています。

そのほかの電子回路やプロセス技術は下記からたどることができます。

プロセス技術

半導体でのプロセスは集積回路などを製造していく工程のことです.

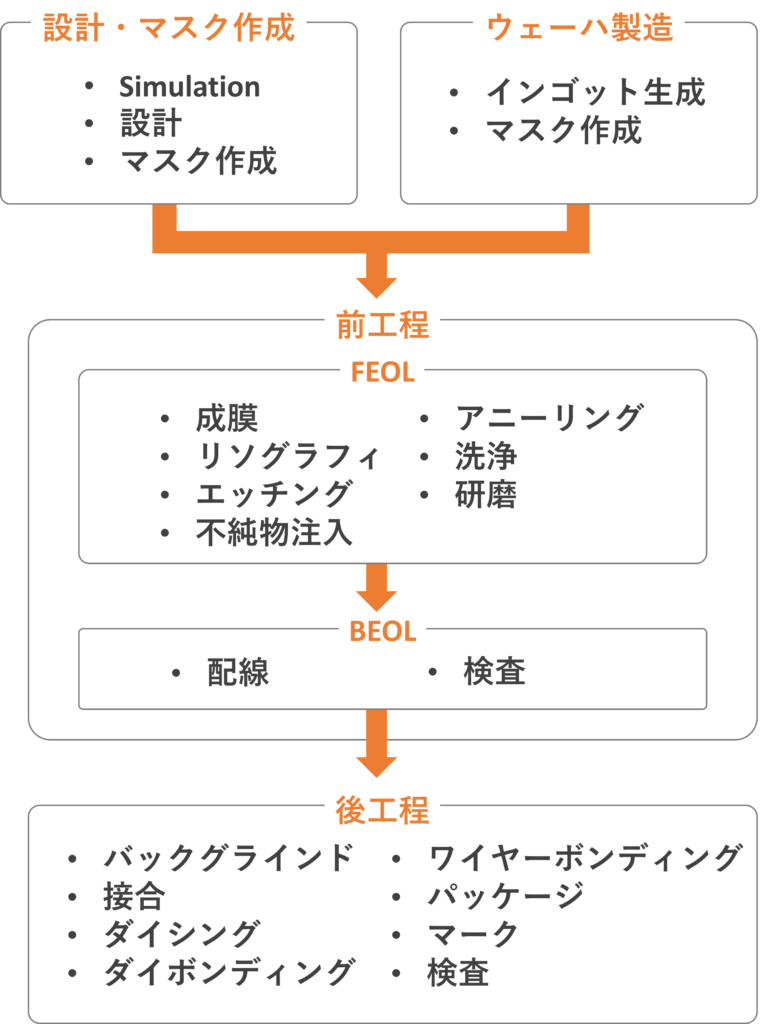

プロセスは以下の図のような順序で行われます.それぞれの工程についての説明は本記事を含めた3つの記事で説明していきますが,大まかな流れを説明します.

まずPCで作成したい回路などのSimulationと設計を行います.設計した集積回路を実際に作るために,回路のパターンが描かれたマスクを作成します.そのマスクをもとに,集積チップの基板となるウェーハに回路などを作っていく工程が前工程です.前工程はさらに,トランジスタを生成するまでのFEOL (Front End Of Line)とそのあとの配線を作るBEOL (Back End Of Line)に分かれます.前工程が終わると集積チップの完成です.その集積チップを実際のデバイスで使えるようにするのが後工程です.

半導体企業

半導体を設計・製造する会社は,垂直統合型 (IDM),ファブレス,ファウンドリーに分けることができます.

垂直統合型 (IDM)は設計→製造→組み立て・検査→販売まですべてを行います.有名な垂直統合型の会社としてはSumsong, Intel, SONYなどがあります.

ファブレス (Fabless)は設計特化の会社で,自分たちで製造はしません.製造はファウンドリーに任せるため,自分たちで製造装置の投資をする必要がなく,また最新の技術を使うことができます.有名なファブレスの会社はApple, Broadcom, Qualcommがあります.

ファウンドリー (Foundry)は製造特化で,他の会社が設計したものを製造する会社です.有名なファウンドリーにTSMC, Global Foundries, UMCがあります.

クリーンルーム

集積チップはとても繊細なものであるため,集積チップの製造は空気中のほこりやゴミ,菌が少ない部屋であるクリーンルームで行います.

ほこりや微粒子 (パーティクル)は集積チップの故障や不具合の原因となるため,クリーンルームのクリーンレベルを上げることで歩留まりを向上させることができます.

クリーンルームのクリーンレベルを上げるためには,「異物を持ち込まない」・「発生させない」・「堆積させない」・「排除する」四原則が重要になります.またクリーン度を示す規格もいくつかあります.

設計・フォトマスク作成

Simlation・設計

集積回路のSimlationと設計は様々なソフトウェアを利用して行います.集積回路や電気・電子デバイスの自動化,支援,補助するためのソフトウェアをEDA (Electronic Design Automation,電子設計自動化ツール)といいます.EDAは電子系のCAE (Computer Aided Engineering),CAD (Computer Aided Design),CAM (Computer Aided Manufacturing)です (電子系以外でもCAE,CAD,CAMがあります).

CAE (Computer Aided Engineering)はコンピュータによるエンジニアリングの支援を行うためのツールで,コンピュータでのシミュレーションや仮想的な解析を行えます.CAD (Computer Aided Design)はコンピュータによる設計を行うためのツールです.CAM (Computer Aided Manufacturing)はコンピュータによる製作の支援をするツールです.

フォトマスク作成

フォトマスク (マスク,レチクル)は集積チップを製造するときのリソグラフィという工程で使用される,回路などのパターンが描かれた透明な板のことです.

基板 (透明な板)の材料はガラスや合成石英,遮光膜 (回路などのパターン)にはクロム (Cr)が使われることが多いです.ガラスは膨張熱による位置の誤差が無視できなくなり,また紫外線を通しにくいため,微細プロセスでは合成石英が使われます.

製造方法は以下の通りです.まず基板 (透明な板)の上にクロム膜を形成して,その上にレジストを塗布します.設計したデータに従って,クロムを除去したい箇所にレーザー露光をし,現像,クロムのエッチング,レジスト剥離することで製造できます.フォトマスクの市場は,凸版フォトマスクなどの日本勢が高いシェアを占めています.

ウェーハ製造工程

ウェーハとはシリコン (Si)などの半導体を薄い円盤状の板にしたもので,集積チップを形成する基板になります.ウェーハ製造の製造方法の例は以下の通りです.

ウェーハの製造方法 (例)

- ウェーハ砕いた高純度の多結晶シリコンを石英るつぼに入れて,加熱して溶かす.このとき,ボロン (B)やリン (P)などの不純物を入れることで,電気低効率を調整する.

- インゴット生成:ワイヤ状の種結晶のシリコン棒を溶解したシリコンの液面につけ,回転させながら引き上げることで,種結晶の同じ原子配列の単結晶のインゴットができる.(CZ法:Czochralski法,チョクラルスキー法).インゴットの生成方法はCZ法以外にも,強力な磁場をかけながら行うCZ法であるMCZ法 (Magnetic field applied Czochralski法),石英るつぼを用いないで,低酸素濃度のインゴットを生成するFZ法 (Floating Zone)などがある.

- スライシング (切断):インゴットの直径が同じになるように外周を研削する.その後,ワイヤーソーなどを用いて,円盤状にスライスする.このスライスされた円盤がウェーハとなる.

- 研磨 (ラッピング):ウェーハの両面を研磨剤を用いて粗く研磨して,厚みのばらつきや歪みを整える.

- エッチング:ウェーハ表面のダメージを取り除くため,化学的なエッチングを行う.

- 熱処理 (アニーリング):熱処理することで,ウェーハの欠陥を低減させる.

- 研磨 (ポリッシング):CMP (Chemical Mechanical Polishing)を用いて,ウェハ表面を平坦化して,鏡面仕上げをする.

- 洗浄・乾燥,検査:加工終了後に異物や汚れを落とすための洗浄・乾燥を行う.その後,検査をして出荷する.

- エピタキシャル・ウェーハ (EW:Epitaxial Wafer) (特殊加工):ウェハ上に新しく単結晶シリコン膜を成長させたウェーハ.この成長させた層はエピタキシャル層と呼ばれる.欠陥の少ないウェーハや,低効率や材料の違う多層構造にしたい場合に用いられる.基板と成長させる薄膜が,同じ物質であるものをホモエピタキシャル,異なる材料であるものをヘテロエピタキシャルという.

- SOIウェーハ (Silicon-On-Insulator Wafer) (特殊加工):シリコンの下に酸化膜の層を設けたウェーハ.酸化させた支持基板と活性基板を熱処理によって貼り合わせて,研磨等をすることで製造する.SOIでは,酸化膜によってトランジスタなどの素子分離が可能.これによってリーク電流を減らしたり,ラッチアップを抑えることができる.

ウェーハのサイズの大口径化が進みました.ウェーハサイズを大きくすると,一つのウェーハで取得できるチップ数が増えて,高効率化によって1チップあたりのコストが低下します.そのため,ウェーハサイズは初期の3インチ程度のものから300ミリへと大口径化が進みました.それより大きいウェーハサイズもありますが,大きいウェーハを利用するためには施設への投資が必要となり,大口径化によって設備投資へのコストも増大しており,今のところ3000ミリ以上のウェーハサイズはあまり利用されていません.

ウェーハには結晶方位を示し,後の工程で位置を決めするための目印があります.ウェーハのサイズが200mmまでの時代では,オリフラ (オリエンテーションフラット,OF)と呼ばれる目印が使われていました.その後はより小さいノッチと呼ばれる目印が使われています.

まとめ

- プロセス技術:集積回路などを製造していく工程.工程は前工程と後工程に分かれる.さらに前工程はFEOLとBEOLに分かれる.

- 半導体企業:半導体企業には設計から製造まですべてを行う垂直統合型 (IDM),設計特化のファブレス (Fabless),製造特化のファウンドリー (Foundry)がある.

- クリーンルーム:集積チップの製造は空気中のほこりやゴミ,菌が少ない部屋であるクリーンルームで行う

- Simulation・設計:集積回路のSimlationと設計は様々なソフトウェアを利用して行う.集積回路や電気・電子デバイスの自動化,支援,補助するためのソフトウェアをEDAという.

- フォトマスク:集積チップを製造するときのリソグラフィという工程で使用される,回路などのパターンが描かれた透明な板.

- ウェーハ:シリコン (Si)などの半導体を薄い円盤状の板にしたもので,集積チップを形成する基板.