この記事では、集積回路とトランジスタ技術の進化に関する重要な情報を詳しく紹介しています。ムーアの法則に基づく微細化の課題から、LDDやFinFET、GAAFETといった最先端技術まで幅広く説明しています。集積回路の進化を深く理解するための参考にぜひご覧いただければ幸いです。

集積回路の概要

集積回路(IC: Integrated Circuit)は、複数の電子部品(トランジスタや抵抗、コンデンサなど)を1つの小さなチップに集めた回路です。これにより、回路の小型化、効率化、性能向上を実現できます。集積回路は、電子機器をコンパクトで高性能にするための基盤技術として非常に重要です。

集積回路の主な必要性は、機器の小型化と高機能化にあります。これにより、デバイスのサイズを小さくしつつ、より多くの機能を搭載することが可能となります。また、製造コストも削減され、信頼性の向上や省エネルギー化にもつながります。これらのメリットにより、集積回路は現代の技術の中心に位置し、ほぼすべての電子機器に欠かせない存在となっています。

集積回路は、コンピュータ、スマートフォン、テレビ、車載システム、医療機器、家電製品など、さまざまな分野で広く応用されています。例えば、スマートフォンの中にはプロセッサ、メモリ、無線通信機能など、複数の機能が集積回路として一つのチップに組み込まれています。また、コンピュータのCPUやグラフィックカードにも集積回路が使用され、情報処理を高速で行っています。このように、集積回路は現代の電子機器の多くで中心的な役割を果たしており、その技術なしには現代の高度な技術社会は成り立たないと言えます。

ムーアの法則・スケーリング則

ムーアの法則

ムーアの法則は米インテル創設者のひとりのゴードン・ムーアが提唱した,集積回路のトランジスタ数が18か月 (周期は様々ある)で2倍になるという経験則です.これは経験則から次第に義務のような法則となり (エンジニア達を苦しめた?),半導体業界を急激に発展させることに繋がりました.微細化もだんだんと難しくなってくるとこの法則も鈍化していき,2010年代後半にはムーアの終焉したともいわれています.

その後もトランジスタの微細化は進んでいきましたが,単純な微細化が難しくなっていくると3次元的な構造にすることで更なる微細化は進んでいきました.このような微細化を進めていくことをMore Mooreといいます.

それとは別に,回路やセンサーなどを混在させることで機能を進化させていくMoor than Mooreもあります.さらに現在のCMOSではなく,別の原理に基づいた集積回路で進化させていくトレンドをBeyond CMOSといいます.集積回路関係のエンジニア・研究者達はこの3つの進化のトレンドを中心に,さらなる発展に挑戦しています.

スケーリング則 (デナード則)

スケーリング則 (デナード則)はトランジスタの微細化をする際に,デバイスでの電界を一定にするためにデバイスの縮尺と電源電圧を\(1/k\),不純物濃度を\(k\)にしていくといろいろといいことがあるよという法則です.

下の表にデナード則に従って微細化した際の各パラメータの変化についてまとめています.表のオレンジ色のようにスケーリングしていくと,青色のようなメリットが出てきます.この他にも微細化することで,同じ性能のものを作るとチップサイズが小さくなります.チップサイズが小さくなるとコストが下がり,歩留まりもよくなるメリットがあります.

| パラメータ | スケーリング比 |

|---|---|

| チャネル長 \(L\) | \(1/k\) |

| チャネル幅 \(W\) | \(1/k\) |

| ゲート酸化膜厚 \(t_{ox}\) | \(1/k\) |

| 不純物濃度 | \(k\) |

| 電源電圧 \(V\) | \(1/k\) |

| 電流 \(I\) | \(1/k\) |

| 容量 | \(1/k\) |

| 回路遅延 | \(1/k\) |

| 消費電力 | \(1/k^2\) |

| 電流密度 | \(k\) |

| 面積 | \(1/k^2\) |

| 電界 \(E\) | \(1\) |

トランジスタ微細化の課題

寄生抵抗・寄生容量・消費電力・遅延・ばらつきの増加

トランジスタを微細化していくと,以下のような寄生抵抗・寄生容量・消費電力・遅延・ばらつきの増加のような課題がでてきます.

- 微細化によって配線・ビアの幅小さくなって寄生抵抗が増えます.寄生抵抗や寄生容量が増えることで消費電力増加や遅延増加になってしまいます.この対策として元々は扱いやすいアルミニウム (Al)を使っていましたが,より抵抗の低い銅 (Cu)を配線に使うようになりました.

- さらに微細が進むとCuのメッキであるバリアやライナーの割合が増えて,この部分の抵抗が問題になりました.この対策としてコバルト (Co)などの他の材料の開発がされています.

- コンタクト小さく,コンタクト抵抗が大きくなってしまう.対策としてシリサイドがあります.

- 配線間距離小さくなるため,寄生抵抗が増えてしまいます.この容量をさげるために,配線間の絶縁体で誘電率の低いLow-k材料が使われつ対策があります.

- ドリフト速度の飽和

- 微細化によってチャネル当たりの不純物の数が少なくなるなどによって,トランジスタのばらつきが大きくなります.

短チャネル効果 (DIBL,パンチスルー)

短チャネル効果 (ショートチャネル効果)はゲート長が短いときに,トランジスタ特性に悪影響を与える現象です.短チャネル効果としてはDIBIとパンチスルーがあります.

微細化が進んでゲート長が短く・ソース・ドレインが深く・ドレイン電圧が大きいと,ゲートによる電界の制御がゲート下深くまで及びづらくなります.これがドレイン誘起障壁低下 (DIBL:Drain-Induced Barrier Lowering)で,ソースからドレインへの障壁が低くなります.これが顕著になって深いところでソース・ドレインがつながってしまうパンチスルーが起きます.これらによってチャネルの開け閉めの制御がうまくできなくなり,特性としてはしきい値 \(V_{th}\)が下がる,サブスレッショルド電流が増大,サブスレッショルド係数 (Sファクタ)が悪くなってサブスレッショルド電流の立ち上がりが遅くなります.

これらを改善するために,LDD,Extension,Haloなどのインプラ (イオン注入)があります.さらに技術が進むとFInFETやAAGFETによってゲート制御性が向上して,短チャネル効果も低減する技術もあります.

故障・特性劣化 (TDDB, HCI)

微細化によってトランジスタの故障もしやすくなります.TDDB (Time Dependence Dielectric Breakdown)は,ゲートに電圧を印加し続けていづれ絶縁破壊を起こしてしまう現象です.微細化が進み,ゲート酸化膜の薄膜化と電界が高くなると,TDDBによる故障が起きやすくなります.

HCI (Hot Carrier Injection)は高電界によって加速されたキャリアがゲート酸化膜中に注入されて,トラップされることでトランジスタ特性が劣化してしまう現象です.これも微細化によって電界が高くなると起きやすくなります.

その他にも微細化によってNBTI(Negative Bias Temperature Instability)やEM (Electromigration:エレクトロマイグレーション)などの故障や特性劣化が顕著になります.

発熱・ダークシリコン問題

微細化によってトランジスタ数増加・集積度向上による消費電力増加で発熱の問題が深刻化してきました.発熱によって使うことができないトランジスタが多く (ダークシリコン問題),集積度が上がるメリットも薄れてしまっています.

開発コスト・計算量あたりの単価の増大

微細化を開発していくには開発コストが必要ですが,微細化が進むにつれて開発コストも高くなっています.そのため採算を取るのが難しくなってきています.

またチップの計算量当たりの単価が微細化によって一部増大してしまっています.そのため微細化のメリットの一つである低コスト化がなくなってきています.

微細化技術

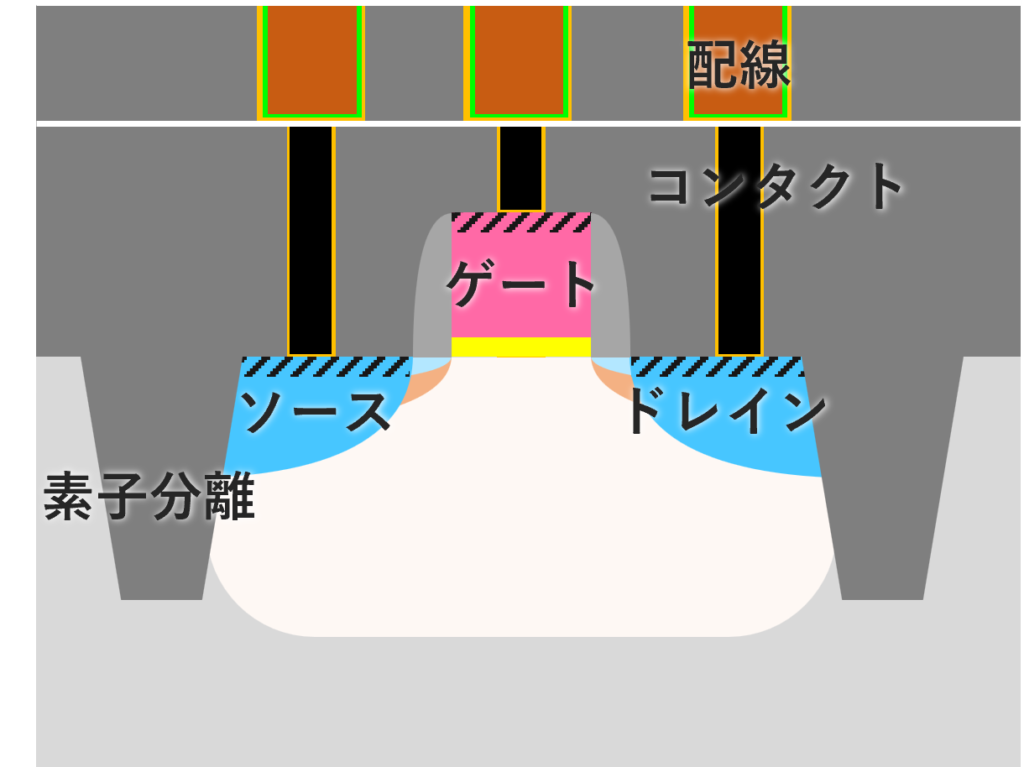

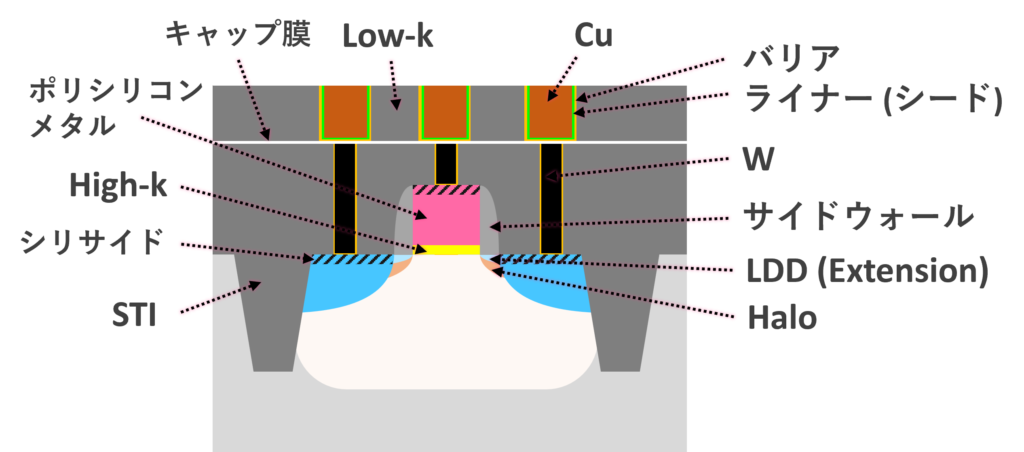

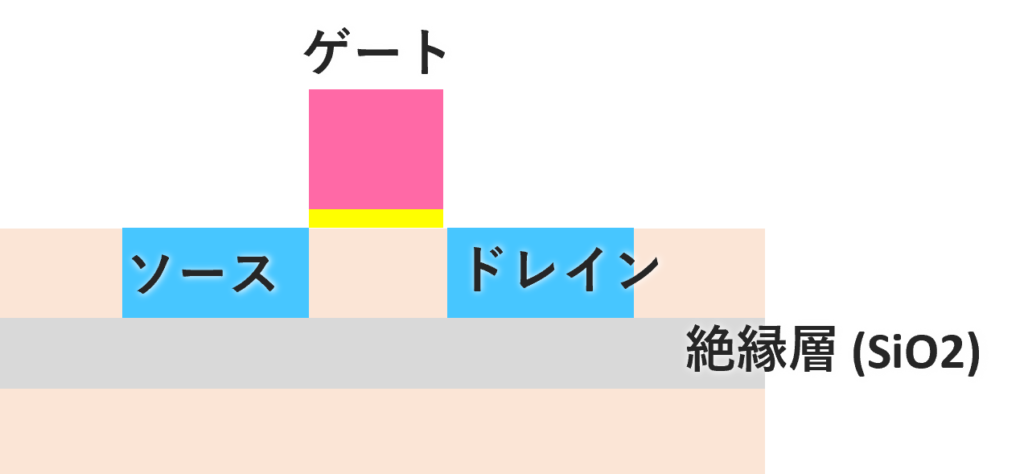

MOSFETは従来のシンプルな構造から,微細化が進んで様々な技術が開発されてきました.下の図のそれぞれの技術を以下で解説していきます.

LDD,Halo

LDD (Lightly Doped Drain,Extension)はドレインとチャネルの間に低濃度の不純物層を設けることで,ここでの電界集中を避ける構造です (ドレイン電界の緩和).これによってホットキャリアによるしきい値変化などを低減して,信頼性を向上させることができます.

Haloはボディー (バルク)より濃い不純物層によって,チャネルの端からの空乏層の侵入を抑制します.これによって短チャネル効果を低減します.Haloに似たPocketという構造もあります.

サイドウォール (スペーサー)

サイドウォール (スペーサー)はゲートの両端に絶縁体の壁を設けた構造体のことです.酸化膜やナイトライド (窒化物)を形成後,異方性エッチングによってサイドウォール形成します.

ソース・ドレインを打ち込むときに,このサイドウォールをマスクとしてソース・ドレインを形成 (SADP:Self-Aligned Double Patterning)することに利用します.

これによってLDDなどを打ち込んだあとに、重ねてソース・ドレインを打ち込みをする際に精度高くでき,LDDなどの調整がより細かくできるようになります.

シリサイド,サリサイド

シリサイド (Silicide)はゲート (ポリシリコン)・ソース・ドレインのコンタクト部を金属化 (シリサイド)することです.これによってコンタクト抵抗を下げることができます.

材料としてはチタン (Ti),コバルト (Co),ニッケル (Ni),タングステン (W)が使われます.シリサイドに似たワードでサリサイドがありますが、サリサイドはSelf Aligned Silicideの略で、自己整合 (Self Aligned)によってシリサイドを形成する技術です.

ゲート技術

ゲートには元々はアルミニウム (Al)が使われていました.

その後は、熱耐性良く、容易に堆積、扱い安さ (金属はシリコン側に拡散の可能性ある)などのメリットから、濃い不純物 (抵抗をさげるため)が添加されたポリシリコン (多結晶シリコン)が使われるようになりました.

微細化が進み、ゲート酸化膜としてHigh-k材料が使われるようになると,ゲートで金属も使われるようになりました (High-k材料の場合はゲートに金属を使う必要がある).材料としてタングステン (W)などが使われます.

ゲート絶縁膜技術

ゲート絶縁膜としては酸化膜 (SiO2)が使われてきました.しかし微細化が進んでいくとゲート絶縁膜が薄くなり,トンネル効果によるリーク電流や信頼性が悪化してきました.

そこで酸化膜やナイトライド (窒化物)と比べて誘電率が高いHigh-k材料もゲート絶縁膜として使われるようになりました.これによって絶縁膜でのリーク電流や信頼性が改善されて,絶縁膜をより薄膜化することができます.材料としてはハフニウム酸化膜,酸化ランタン膜などがあります.High-k材料とポリシリコンは相性が悪いため,High-k材料にはゲート金属を使用する必要があります.そのためHigh-kと金属ゲートはセットで説明されることが多いです.

素子分離

トランジスタを単体を動作させるためには,トランジスタ同士を素子分離 (Isolation)する必要があります.よく使われる素子分離にLOCOS(LOCal Oxidation of Silicon)とSTI (Shallow Trench Isolation)があります.

LOCOSは部分的に酸化させることで素子分離させます.しかし細かな制御難しいことや段差ができてしまう欠点からSTIが多く使われるようになりました.STIは一度,溝を作ってから,そこに酸化膜を埋め込むことで素子分離させます.

コンタクト・配線技術

従来,配線にはアルミニウム (Al)が使われてきました.しかし微細化が進んで寄生抵抗が問題になってくると,抵抗を下げために配線に銅が使われるようになりました.また銅はEM (エレクトロマイグレーション)の点でもメリットがあります.

なぜもともと銅が使われていなかったかというと,銅はシリコンにしみ込みやすくショートしてしまう可能性があり,またエッチングによる配線がも困難で扱いにくい材料だからです.

これを解決するために様々な工夫がされています.まず製造上の工夫としてダマシンで配線をします.ダマシンでは一度配線が入る穴を開けます.そこにメッキなどをした上で銅を全面に埋めます.そして上から余分な銅を削ることで配線を形成します.

次に浸み込み対策です.図にもあるように配線間にキャップ膜を設けることでしみ込みを防ぎます.また配線を作る前に事前にバリアメタルとライナーがメッキされます.バリアメタルは銅をしみ込みを防ぐ役割があり、ライナーは銅を充填させるのを容易にする効果があります.これらの材料としてチタン系 (Ti)やタンタル系 (Ta),コバルト系 (Co)が使われます.

さらに微細化が進むと比較的に抵抗の高いバリアメタルやライナーの比率が増えて銅による抵抗率低減の効果が下がってしまいます.そこで配線にコバルト系などの別の材料も開発されています.

コンタクトにはタングステン (W)などが使われます.

Low-k

微細化で配線間が近くなることによる寄生容量増加の対策として、配線間の絶縁体に容量に小さいLow-kの材料を使うことで寄生容量を下げることができます.これによって高速化・低消費電力化のメリットがあります.

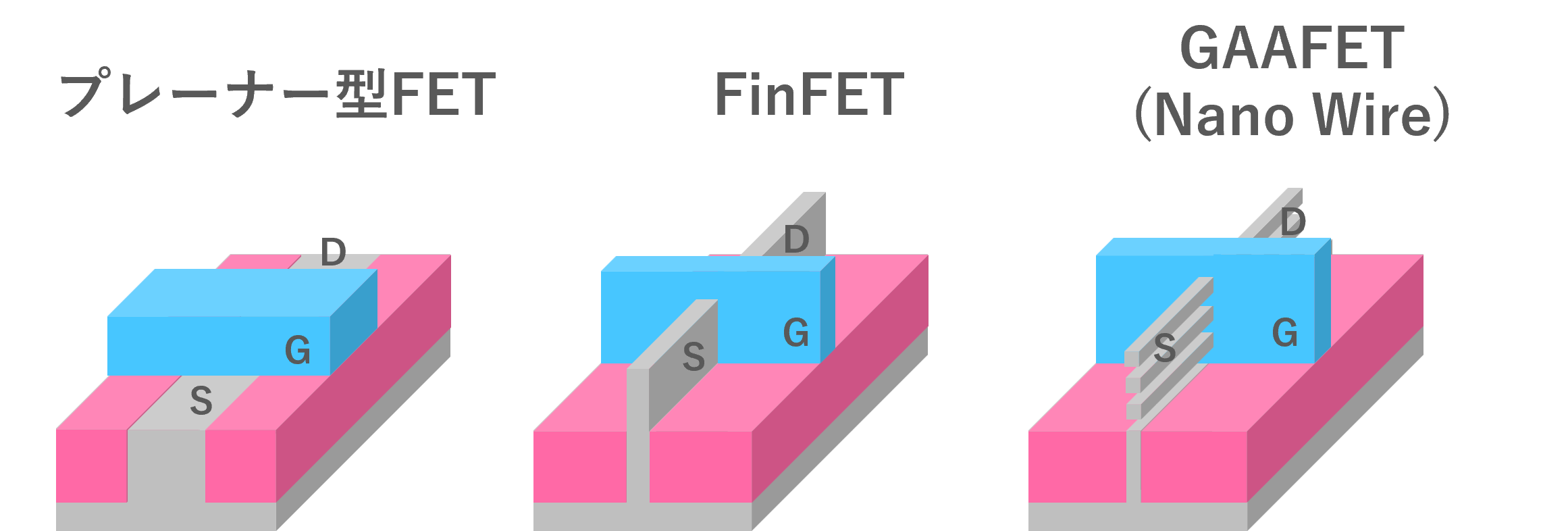

微細化トランジスタ構造の進化 (プレーナー型,FinFET,GAAFETなど)

教科書にあるような基本的なMOSFETはプレーナー型FET (~28nm世代)と呼ばれます.プレーナー型での微細化が厳しくなってくると,上図のようなFinFET (2nm世代~5nm世代)に構造が進化しました.この構造によって実質的な面積が増えて制御しやすくなって,リーク電流低減や高速などのメリットがあります.

これがさらに進化した構造がGAA (Gate All Around)FET (3nm世代~)です.上図ではNano Wire (ナノワイヤー)のGAAを示しています.これがさらに進化した構造がNano Sheet (ナノシート)のGAAです.

この他にも垂直にワイヤーが伸びているVertical Nano Wireや,3次元にFETが複雑に積み重なったStacked CMOSなど,さらなる進化を目指すMOSFETの構造があります.

その他の集積・トランジスタ技術

SOI (Silicon On Insulator)

SOI (Silicon On Insulator)はトランジスタの下に絶縁層 (Insulator)を設けた構造をしています.この構造によって寄生容量が減り,高速化・低消費電力化につながります.

MEMS

MEMS (Micro Electro Mechanical Systems)は機械的動作を集積したデバイスです.機械的観点からみると今まで大きかった機械をIC上にすることができます.電子工学的観点からいうと通常の集積回路では実現できないことができるようになります.

MEMSの例としてDMD (デジタルミラーデバイス),圧力センサー,プリンターヘッド,磁気ヘッド,ジャイロスコープなど様々な応用があります.

HEMT

HEMT (High Electron Mobility Transistor: 高電子移動度トランジスタ)は,ヘテロ接合 (異材料の接合)によって誘起された高移動度をもつガス層 (ヘテロ接合によってチャネル部が分離)がチャネルの電界効果トランジスタです.一般的に化合物半導体が用いられ,より高速で低ノイズの特徴を持ちます.

Si以外の半導体

半導体はシリコン以外にもたくさんあります.半導体の種類によっても特徴があります.以下に主要・注目の半導体と簡単にそれぞれの特徴を示します.

- シリコン (Si):最も使われる.資源豊富.扱いやすい.低コスト

- ゲルマニウム (Ge):高移動度.

- 炭素 (ダイヤモンド) (C):高性能.低消費電力.熱伝導率高い.扱いにくい.高コスト.

- 化合物半導体 (SiC,GaNなど):欠陥が多い.割れやすく大判化が難しいため高価.

- 炭化ケイ素 (SiC):パワー半導体.

- 窒化ガリウム(GaN):青色LED.パワー半導体.高周波.高効率.

- ヒ化ガリウム (GaAs):レーザー・LED.高周波.

- リン化インジウム (InP):レーザー・LED.高周波.

SoC・SoP・3次元LSI (積層)

トランジスタの技術を開発していく以外にも,複数の機能を一つのチップやパッケージに搭載する,複数のチップを積層することなどでも性能を上げることができます.

- SoC (System on Chip):様々な機能を一つのチップに搭載したもの.小型化,低消費電力,高効率,高速化のメリットがある.開発に時間とコストがかかるデメリットがあり.

- SiP (System in Package):別のチップを一つのパッケージに搭載したもの.小面積,小型化のメリットがある.SoCは別のメリットがあるため,両方使われることもある.

- 3次元LSI (積層):チップを3次元に積層したものです.大きなチップにするよりも積層することで面積を小さくすることができる.積層方法は以下のように様々ある.

- CoC (Chip on Chip):チップをチップの上に積層.

- CoW (Chip on Wafer):チップをウエハー上に積層してから分離.

- WoW (Wafer on Wafer):ウエハーの上にウエハーを積層.

- CoF (Chip on Film):フィルムに直接チップを搭載.フレキシブル.

まとめ

- ムーアの法則:集積回路のトランジスタ数が18か月 (周期は様々ある)で2倍になるという経験則

- スケーリング則 (デナード則):デバイスの縮尺と電源電圧を1/k,不純物濃度をkにしていくといろいろメリットがある法則

- トランジスタ微細化課題:寄生抵抗,寄生容量,消費電力,遅延,ばらつき増加,短チャネル効果,故障・特性劣化,発熱,ダークシリコン問題,開発コスト・計算単価あたりのコスト増加など

- 微細化技術:LDD,Halo,サイドウォール,シリサイド,ゲート技術,ゲート絶縁膜技術,素子分離,コンタクト・配線技術,Low-kなど

- その他の集積・トランジスタ技術:SOI,HEMT,MEMS,Si以外の半導体,SoI,SiP,3次元LSI (積層)などの様々な技術がある

- 微細化トランジスタ構造の進化:プレーナー型→FinFET→GAAFETへと微細化トランジスタが進化している